# Extending the small-signal modeling of GFETs to ambipolarity regime

Nikolaos Mavredakis, Anibal Pacheco-Sanchez, David Jiménez

N. Mavredakis, A. Pacheco and D. Jiménez are with the Departament d'Enginyeria Electrònica, Escola d'Enginyeria, Universitat Autònoma de Barcelona, Bellaterra 08193, Spain. (e-mail: Nikolaos.mavredakis@uab.cat).

### 1. Abstract

Analog/RF circuit design with Graphene field-effect transistor (GFET) technology, continually grows due to exceptional extrinsic maximum oscillation (fmax) and cut-off frequencies  $(f_t)$ , recorded for the specific device [1]. We have recently proposed an efficient small-signal GFET parameter extraction procedure, targeting on Quasi-Static regime [2]. Our methodology is based on a charge-based model [3] which ensures charge conservation in the intrinsic device. Both the bias- and frequency- dependence of the total of small-signal parameters have been accurately validated with experiments from a short-channel RF CVD GFET [4], up to 18 GHz for a unipolar (p-type) region of operation. In the present study, the complete ambipolar small-signal response of short-channel GFETs [5], [6] is demonstrated, including the charge neutrality point or Dirac voltage (V<sub>Dirac</sub>), with remarkable agreement between models and experiments. The bias region around V<sub>Dirac</sub> is of outmost significance in certain applications of ambipolar devices such as GFET, as it can ensure multifunctionality [7].

## 2. DUT and Measurement Setup

High frequency measurements are conducted in the present work for two short-channel back-gated RF CVD GFETs with gate width W=12x2 µm (number of gate fingers:2) and gate length L=200 nm, 300 nm, respectively [5], [6]. They are fabricated by the same group as the device studied in [2], but from a different technology process and thus, they present dissimilar characteristics such as higher contact resistance R<sub>C</sub>. They have also been examined in terms of thermal noise experimental characterization and modelling at 1 GHz [6]. In the current work, S(Y) parameters are measured and small-signal parameters are investigated after appropriate de-embedding and R<sub>C</sub>-gate resistance R<sub>G</sub> elimination procedures [8], [2], [6] up to or even above ft. Details on the devices' schematics and measurement setups can be found in [5], [6].

## 3. Results and Discussions

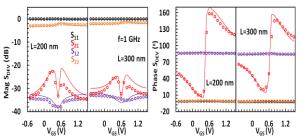

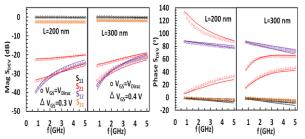

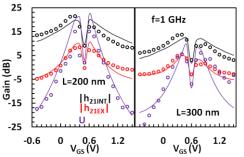

The small-signal sub-circuit model employed in this study, has been presented elsewhere [2 (Fig. 1a)]. As a first step of this work, IV model parameters are extracted, similarly as in [2], for both devices under test (DUT), and presented in Table I; µ is the carrier mobility,  $C_{back}$  the back-gate capacitance,  $\Delta$  the inhomogeneity of the electrostatic potential, related to the residual charge, u<sub>sat</sub> the saturation velocity while the rest of the parameters (V<sub>Dirac</sub>, R<sub>C</sub>, R<sub>G</sub>) have already been defined. Magnitude and phase of all the measured SDEV parameters for both DUT at a drain voltage V<sub>DS</sub>=0.5 V, are presented vs. V<sub>GS</sub> at 1 GHz (cf. Fig. 1) and vs. frequency at two V<sub>GS</sub> values (cf. Fig. 2), near and exactly at V<sub>Dirac</sub> point, respectively (V<sub>GS</sub>=0.3, 0.5 V for L=200nm,  $V_{GS}$ =0.4, 0.6 V for L=300 nm). The consistency of the extracted models is also highlighted from p- to n-type region including V<sub>Dirac</sub>, while observed disparities at higher frequencies (cf. Fig. 2) arise from non-quasi-static (NQS) effects due to low ft of the devices [9]. The recorded model agreement with experiments at V<sub>Dirac</sub> is prerequisite for reliable circuit design in RF GFET applications such as phase/frequency configurable amplifiers, frequency doublers, in-phase power and inverting amplifiers, which operate near or at the specific neutrality point [7]. Inconsistencies observed in the magnitude of S<sub>21DEV</sub> at n-type region are due to measurement asymmetries between hole and electron branches, and can be accounted by considering distinct models for the two conductance regimes [9].

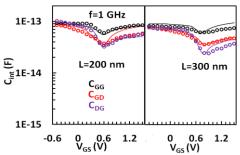

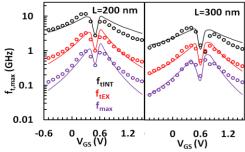

After rigorous removal of R<sub>C,G</sub> contributions, intrinsic small-signal parameters of the DUT, such as capacitances CGG, CGD, CDG, cut-off frequency ftINT, and small-signal current gain |h<sub>21INT</sub>|, can be extracted [2]. Other significant extrinsic figures of merit, such as ftEX,  $|h_{21EXT}|$ , and unilateral power gain U, can also be derived directly from de-embedded  $S(Y)_{DEV}$  measurements [2]. C<sub>GG</sub>, C<sub>GD</sub>, C<sub>DG</sub> (cf. Fig. 3), f<sub>tINT.EX</sub>, f<sub>max</sub> (cf. Fig. 4), and |h<sub>21INT,EX</sub>|, U (cf. Fig. 5), are depicted for both DUT at 1 GHz for  $V_{DS}=0.5$  V, vs.  $V_{GS}$  where the models capture precisely the experiments, especially around V<sub>Dirac</sub>, which is of special interest in the current analysis. Intrinsic capacitances present a minimum at V<sub>Dirac</sub> and afterwards, increase towards higher carrier densities. Besides, ftint, EX, fmax, h21INT, EX, U parameters follow an M-shape trend with a minimum at V<sub>Dirac</sub> while, they are significantly reduced (for the L=300 nm device) in comparison with a GFET with same L but much lower  $R_{\rm C}$  in [2]. The latter highlights the negative effect of  $R_{\rm C}$ on small-signal parameters and thus, justifies the aforementioned NQS effects below 5 GHz (cf. Fig. 2).

Table 1. IV extracted parameters

| 1                  |                    |                   |                   |

|--------------------|--------------------|-------------------|-------------------|

| Parameter          | Units              | L=200 nm          | L=300 nm          |

| μ                  | $cm^2/(V \cdot s)$ | 200               | 170               |

| usat               | m/s                | 7x10 <sup>5</sup> | 7x10 <sup>5</sup> |

| Cback              | µF/cm <sup>2</sup> | 1.87              | 1.87              |

| V <sub>Dirac</sub> | V                  | 0.5               | 0.6               |

| Rc                 | Ω                  | 130               | 180               |

| R <sub>G</sub>     | Ω                  | 18                | 12                |

| Δ                  | meV                | 150               | 165               |

Fig. 1. Magnitude (left plot) and phase (right plot) of deembedded S-parameters (S<sub>DEV</sub>) for two GFETs with gate width W=24  $\mu$ m and length L=200 nm (left subplots), L=300 nm (right subplots) vs. gate voltage V<sub>GS</sub> for operation frequency f=1 GHz at a drain voltage V<sub>DS</sub>=0.5 V. Markers: measurements, lines: model.

Fig. 2. Magnitude (left plot) and phase (right plot) of deembedded  $S_{DEV}$  for two GFETs with W=24  $\mu$ m and L=200 nm (left subplots), L=300 nm (right subplots) vs. f for two V<sub>GS</sub> values; near and at Dirac Voltage at V<sub>DS</sub>=0.5 V. Markers: measurements, lines: model.

Fig. 3. Intrinsic capacitances  $C_{GG}$ ,  $C_{DD}$ ,  $C_{DG}$ , respectively for two GFETs with W=24  $\mu$ m and L=200 nm (left subplot), L=300 nm (right subplot) vs.  $V_{GS}$  for f=1 GHz at  $V_{DS}$ =0.5 V. Markers: measurements, lines: model.

#### Acknowledgements

This work has received funding from the European Union's Horizon 2020 research and innovation programme under grant agreement No GrapheneCore3 881603 and from Ministerio de Ciencia, Innovacion y Univer- ' sidades under grant agreements RTI2018-097876-B-C21(MCIU/AEI/FEDER, UE), FJC2020-046213-I and PID2021-127840NB-I00 (MCIN/AEI/FEDER, UE).

Fig. 4. Intrinsic, extrinsic cut-off and extrinsic maximum oscillation frequencies  $f_{\rm INT}$ ,  $f_{\rm tEXT}$ ,  $f_{\rm max}$ , respectively for two GFETs with W=24  $\mu$ m and L=200 nm (left subplot), L=300 nm (right subplot) vs. V<sub>GS</sub> at V<sub>DS</sub>=0.5 V. Markers: measurements, lines: model.

Fig. 5. Intrinsic, extrinsic small-signal current gain and unilateral power gain  $|h_{21INT}|$ ,  $|h_{21EX}|$ , U, respectively for two GFETs with W=24  $\mu$ m and L=200 nm (left subplot), L=300 nm (right subplot) vs. V<sub>GS</sub> for f=1 GHz at V<sub>DS</sub>=0.5 V. Markers: measurements, lines: model.

#### References

M. Saeed, P. Palacios, M. D. Wei, E. Baskent, C. Y. Fan, B. Uzlu, K. T. Wang, A. Hemmetter, Z. Wang, D. Neumaier, M. C. Lemme, and R. Negra, Adv. Mater., vol. 34(48), 2108473, 2022.

[2] N. Mavredakis, A. Pacheco-Sanchez, W. Wei, E. Pallecchi, H. Happy, and D. Jiménez, Microelectronics J, vol. 133, 105715, 2023.

[3] F. Pasadas, P. C. Feijoo, N. Mavredakis, A. Pacheco-Sanchez, F. A. Chaves, and D. Jiménez, Adv. Mater., vol. 34(48), 2201691, 2022.

[4] W. Wei, D. Fadil, E. Pallecchi, G. Dambrine, H. Happy, M. Deng, S. Fregonese, and T. Zimmer, in Proc. IEEE Int. Conf. Noise Fluctuations (ICNF), Vilnius, Lithuania, 2017.

[5] W. Wei, X. Zhou, G. Deokar, H. Kim, M. M. Belhaj, E. Galopin, E. Pallecchi, D. Vignaud, and H. Happy, IEEE Trans. Electron Devices, vol. 62(9), pp. 2769-2773, 2015.

[6] N. Mavredakis, A. Pacheco-Sanchez, P. Sakalas, W. Wei, E. Pallecchi, H. Happy and D. Jiménez, IEEE Trans. on Microw. Theory Tech., 69(11), pp. 4639-4646, 2021.

[7] A. Pacheco-Sanchez, J. N. Ramos-Silva, N. Mavredakis, E. Ramirez-Garcia, and D. Jiménez, in proc. IEEE Conf. on Design of Circuits and Integrated Circuits (DCIS), Pamplona, Spain, 2022.

[8] J. N. Ramos-Silva, A. Pacheco-Sánchez, M. A. Enciso-Aguilar, D. Jiménez, and E. Ramírez-Garcia, Semicond. Sci. Technol., vol. 35(4), 045024, 2020.

[9] J. D. Aguirre-Morales, S. Fregonese, C. Mukherjee, W. Wei, H. Happy, C. Maneux, and T. Zimmer, IEEE Trans. Electron Devices, vol. 64(10), pp. 4302-4309, 2017.