# Noise impact on memristor performance: improvement of neuromorphic binary STDP

E. Salvador<sup>1</sup>, R. Rodriguez<sup>1</sup>, E. Miranda<sup>1</sup>, J. Martin-Martinez<sup>1</sup>, A. Rubio<sup>2</sup>, V. Ntinas<sup>2</sup>, G. Ch. Sirakoulis<sup>3</sup>, A. Crespo-Yepes<sup>1</sup>, M. Nafria<sup>1</sup>

<sup>1</sup>Electronic Engineering Department, Universitat Autònoma de Barcelona, 08193 Bellaterra, Spain

<sup>2</sup>Electronic Engineering Department, Universitat Politècnica de Catalunya, 08034, Barcelona, Spain

<sup>3</sup>Dept. of Electrical & Computer Engineering, Democritus University of Thrace, 67100, Xanthi, Greece email: emili.salvador@uab.cat

# **ABSTRACT**

Stochastic Resonance (SR) phenomenon has been experimentally observed in Hf-based memristors. The addition of an external noise increases the OFF/ON resistances ratio of the current-voltage (I-V) memristor characteristic. The SR impact on the binary spike time dependent plasticity (STDP) learning rule, when implemented in memristors, has been experimentally analyzed. The two memristor conductance states, which represent the synaptic weights in neuromorphic systems, can be better distinguished if Gaussian noise is added to the bias signal.

## INTRODUCTION

Memristors are of great interest in a wide range of applications due to their properties, as low power consumption and large integration density [1]. Memristors exhibit non-linear current-voltage characteristic, so that the properties associated to nonlinear systems can be explored in these devices. In nonlinear systems, noise can have a beneficial role, improving the device performance. This phenomenon is often referred to as stochastic resonance (SR) and it is present in nature in fields as biology, physics, engineering, etc [2-3]. In memristor-based neuromorphic computing spike time dependent plasticity (STDP) learning approach is commonly accepted in the scientific community as a descriptor of the biological synapse [4]. In this work, we analyze the effect of adding an external noise to the memristor bias on binary STDP, where only '1' or '0' values are assigned for each synaptic weight [4].

# STOCHASTIC RESONANCE IN MEMRISTORS

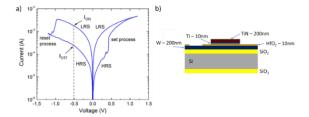

Fig. 1 shows the used memristor structure [5] and a typical I-V curve. From 200 I-V cycles, statistical characterization of the resistance ratio

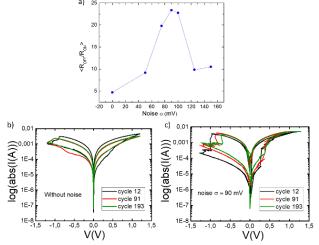

between the OFF and ON memristor states ( $R_{OFF}/R_{ON}$ ) in the presence of noise is performed [6]. Gaussian noise, whose standard deviation ( $\sigma$ ) ranged between 50 mV and 150 mV, is introduced. Fig. 2.a shows that the addition of noise increases the mean values of  $R_{OFF}/R_{ON}$ , and the typical SR curve is observed. The memristor I-V curves without adding noise (Fig.2.b) and with a noise of 90 mV  $\sigma$  summed to the bias (Fig.2.c) show that the memristor I-V characteristic is clearly more open when noise is added, leading to the larger  $R_{OFF}/R_{ON}$  resistance ratios.

## Noise-Induced Binary STDP

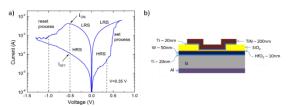

Samples used in this study slightly differ from the previously ones (Fig. 3). To switch devices conductance, set and reset pulses were applied, constructed from the difference between a pulse applied to the top electrode (pre-synaptic pulse, V<sub>pre</sub>) and a pulse applied to the bottom electrode (post-synaptic pulse, V<sub>post</sub>) (Fig 4.a). Conductance state was registered, at a reading voltage,  $V_{read} =$ -0.5V.The reset pulse ( $V_{reset}$ ) is always a 150ms pulse of -1V, to ensure the reset process (Fig. 4.b). For the set pulse (V<sub>set</sub>), lower voltage than the one needed to trigger the set process is applied, in this case V<sub>set</sub>=0.35V. V<sub>set</sub> amplitude is changed every 20 cycles by delaying the post-synaptic pulse (Figure 4.c), generating different overlap situations [7]. Noise addition (with  $\sigma_{noise} = 150 mV$ )) becomes essential for the identification of the two resistive states: when noise is not added, there is no state separation (Fig. 5.a), whereas, with the inclusion of noise (Fig. 5.b), an increase in the mean current after the set pulses, proportional to the overlap between the pre- and post-synaptic pulses (Fig. 5c), is observed.

#### CONCLUSION

The beneficial role of an external noise in the performance of HfO<sub>2</sub> based memristors is

experimentally demonstrated. Noise inclusion increases the OFF/ON resistance ratio and the typical SR curve is obtained. This work presents a first experimental approach for the evaluation of SR in memristors-based neuromorphic systems. The noise addition allows the switching between two resistance states, not initially identified without noise, being the OFF/ON resistance ratio proportional to the pre- and post-synaptic pulses overlap. Further studies on the exploitation of the SR phenomenon in neuromorphic systems are mandatory to perform.

#### ACKNOWLEDGMENT

Spanish The authors acknowledge the MCIN/AEI/10.13039/501100011033, Project PID2019-103869RB and The 'Departament de Recerca i Universitats de la Generalitat de Catalunya'.

### REFERENCES

- I.H. Im et al., Advanced Intelligent Systems, 2020.

- R Benzi et al., Journal of Physics A: Mathematical and General, 1981.

- K. Wiesenfeld el al., Nature, 1995. C. Mohan et al., ISCAS 2021

- S. Poblador et al., Microelectronic Engineering, 2018.

- R. Rodriguez et al., ISCAS 2021.

- E. Salvador et al., IEEE NANO, 2022.

Fig. 1: Typical I-V characteristic (left) and device structure (right) of the memristors used to study the impact of SR on memristors I-V.

Fig. 2: a) Mean memristor ratio  $R_{OFF}/R_{ON}$  as a function of the noise  $(\sigma)$ . The typical stochastic resonance curve is observed. Memristor I-V curves at cycles 12, 91 and 193 b) without and c) with 90 mV noise  $\sigma$ .

Fig. 3: Typical I-V characteristic (left) and device structure (right) of the memristors used to study noise-induced binary STDP.

Fig. 4: a) Pre- and post-synaptic pulses were applied to the top and bottom memristor electrodes, respectively b) voltage waveform (cycle) applied to measure the set and reset currents (20 times) for a given Vset. (c) Amplitude and duration of Vset has been changed by delaying the post-synaptic pulse. Solid lines: pre- and post-synaptic pulses, without overlapping. Dashed lines: examples of delayed post-synaptic pulses.

Fig. 5: Current during the 20 cycles for each  $\Delta t$  shift (post-synaptic pulse delay) and mean current evaluated after a set pulse (orange) and after a reset pulse (blue) a) for the case w/o noise and b) adding a  $\sigma$  = 150mV Gaussian noise. c) Mean resistance ratio versus the postsynaptic pulse delay without noise (blue) and with noise (orange).